太书面化的话我就不说了啊,有些东西就像书上写的,真的看着看着就想睡觉了,还是大白话直白哈。

本文引用地址:http://www.eepw.com.cn/article/267376.htm1、关于触发器的分类

触发器呢大体可以按这几个部分分类:1、按晶体管性质分,可以分为BJT集成电路触发器和MOS型集成电路触发器。2、按工作方式分,可分为异步工作方式和同步工作方式,异步工作方式也就是不受时钟控制,像基本RS触发器,同步方式就是受时钟控制,称为时钟触发器。3、按结构方式分,可分为维持阻塞触发器,延边触发器,主从触发器等。4、按逻辑功能分,可分为RS触发器,JK触发器,D触发器,T触发器,T'触发器等。

2、关于触发器的逻辑功能

触发器总体来说有四种功能:分别是置“0”、置“1”、保持、翻转。前两个不说了,就是高低电平,保持就是维持原状态不变,翻转就是从原状态变为他的反状态。

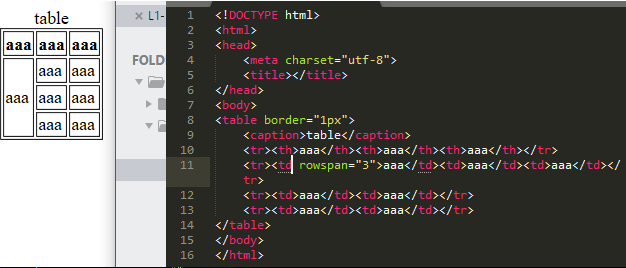

3、基本RS触发器

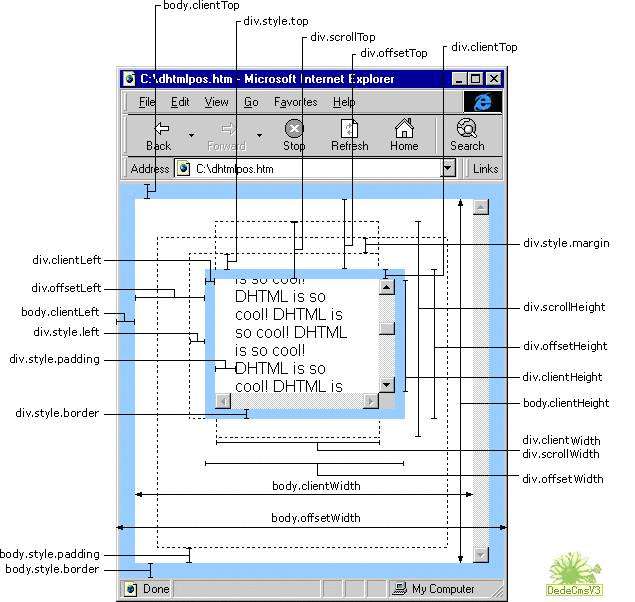

这是基本RS触发器原理图,具体工作原理就不写了吧,个人觉得比较好理解,就说几个我刚开始看的时候有些看不懂的地方吧。

1、关于负脉冲和低电平

所谓负脉冲呢,就是一个信号从高电平置为低电平,然后延迟一段时间后再置为高电平的过程,就像上图所示的脉冲。而低电平就没有返回高电平的过程。

2、关于Q端

我们知道不管是置“1”端还是置“0”端,操作的都是Q端,间接操作Q非端,刚开始我就错误的以为Sd非端控制相应上面的端口,其实不是,Rd非端和Sd非端都是控制Q端,即Sd非端一个负脉冲,Q端置“1”,Q端如果原状态就是“1”,则加一个负脉冲后原状态不改变。Rd非端一个负脉冲,Q端置“0”,Q端如果原状态就是“1”,则加一个负脉冲后原状态不改变。

3、两个端口都加负脉冲的情况下

按理说两个端口是不允许同时加负脉冲的,因为一旦两端同时加负脉冲,则两个输出端就都为“1”,这样与我们认为的两个输出端的值互为反变量的原则就相违背了,但是在画时序图的时候,可以将两个输出端同画为高电平。重点是,当两个输入端都为低电平的时候,再把它们扳回高电平时,这时候输出端就会有两种结果,具体是哪种结果,这要取决于两个门电路的运转速度问题了。下面是时序图

下面是基本RS触发器的真值表

4、同步RS触发器

同步RS触发器是在基本RS触发器的基础上加了两个与非门,CP是时钟。

当CP为“0”时,下面两个门电路相当于被封死,这时第一级门电路的输出端就都为"1",即保持状态。当CP为“1”时,门电路被打开,第一级门电路的输出端分别为Rd非和Sd非,这就和刚才的基本RS触发器一样了。

5、JK触发器

JK触发器的内部原理比较复杂,对于初学者来说,我觉得直接记住他的功能就可以了,这样不至于越学越迷糊,当然有条件的朋友也可以自己去弄明白其中的原理

这是JK触发器的逻辑符号,其中C1代表时钟,左边那个箭头代表负脉冲有效,也就是说只有在时钟负脉冲来临的时候Q端才会发生变化(同步工作的情况,异步除外),R,S端为强制置“0”、“1”端,这两个端口不受时钟控制,可以强迫置位,R端负脉冲置“0”,S端负脉冲置“1”,J、K端为信号端。

这张是JK触发器真值表,可以看出当R、S端都为“1”的情况下,信号端的J、K才会发挥作用,从上到下依次是“保持”、置“0”、置“1”、翻转。

这样就可以得到JK触发器的特性表,有了这个表,我们就可以写出他的特性方程

即

这是时序图,注意Q端只在时钟下降沿出变化

6、D触发器

这是D触发器的逻辑符号,注意时钟是高电平有效,R、S端是强迫置位端,D为信号端

D触发器比较简单,真值表见下图

7、T触发器

真值表

8、T‘触发器

特性方程

T’触发器的重要应用,可以用作分频

9、最后展示一下我之前的作品,呵呵..

京公网安备 11010802041100号

京公网安备 11010802041100号