F2833x Serial Communication Interface

簡介

串行通信接口(SCI)模塊是一個串行I / O端口,允許F2833x與其他外圍設備之間的異步通信。 它通常被稱為UART(通用異步接收器發送器),通常根據RS232標準使用。

SCI接收器和發送器每個都有一個16深的FIFO,用於減少服務開銷,每個FIFO都有自己獨立的使能和中斷位。 兩者都可以獨立操作以進行半雙工通信,或同時進行全雙工通信。

為了保持數據完整性,SCI檢查接收到的數據是否存在中斷檢測,奇偶校驗,溢出和幀錯誤。 通過16位波特選擇寄存器,可以針對不同的通信速率對比特率進行編程。

SCI Data Format

基本數據單元稱為字符,長度為1位到8位。 每個數據字符都使用起始位,1或2個停止位,可選的奇偶校驗位和可選的地址/數據位進行格式化。 數據字符及其格式化位稱為幀。 幀被組織成稱為塊的組。 如果SCI總線上存在兩個以上的串行端口,則數據塊通常以地址幀開始,該地址幀指定由用戶協議確定的數據的目標端口。

起始位是每幀開始時的低位,標記幀的開始。 SCI使用NRZ(非歸零)格式,這意味著在非激活狀態下,SCIRX和SCITX線將保持高電平。 當外圍設備沒有在各自的線路上接收或發送時,它們會將SCIRX和SCITX線路拉到高水平。'

注意:如果您正在使用RS232接口,則串行線路上的所有電壓電平都由外部接口電路驅動,例如Texas Instruments MAX3221。 邏輯“0”作為+5和+ 15V之間的電壓傳輸,邏輯“1”作為-5和-15V之間的負電壓傳輸。 在接收器側,高於+ 3V的電壓將被識別為有效的“0”,低於-3V的電壓將被識別為邏輯“1”。

SCI Data Timing

SCI異步通信格式使用單線(單向)或雙線(雙向)通信。 在此模式下,幀由起始位,1到8個數據位,可選的偶數/奇數奇偶校驗位以及一個或兩個停止位組成(如幻燈片9-3所示)。 每個數據位有8個SCICLK週期。

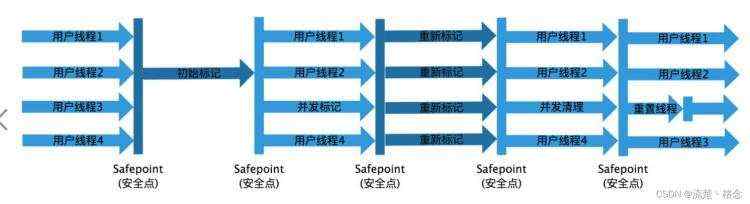

接收器在接收到有效起始位時開始操作。 有效起始位由四個連續的零位內部SCICLK週期標識,如幻燈片9-4所示。 如果任何位不為零,則處理器重新開始並開始尋找另一個起始位。

對於起始位之後的位,處理器通過在位中間產生三個樣本來確定位值。 這些採樣發生在第四,第五和第六SCICLK週期,並且位值確定基於多數(三分之二)。 幻燈片9-4說明了這種異步通信格式,其中一個起始位顯示了多數表決的位置。 由於接收器使其自身與幀同步,因此外部發送和接收設備不必使用同步的串行時鐘。 時鐘可以在本地生成。

SCR Register Set

SCI Communications Control Register (SCICCR)

上一張幻燈片解釋了SCI數據幀結構的設置。

如果未使用多處理器喚醒模式,則應清除第3位。這樣可以避免在數據幀末尾生成額外的地址/數據選擇位(見幻燈片9-3)。

某些主機或其他設備無法處理此額外位。

SCI Control Register 1(SCICTL1)

配置SCICCR寄存器時,SCI端口應首先保持無效狀態。

這是使用SCI控制寄存器1(SCICTL1.5)的SW RESET位完成的。向該位寫入0會初始化並保持SCI狀態機和操作標誌處於復位狀態。

然後可以配置SCICCR。然後,通過向SW RESET位寫1來重新使能SCI端口。在系統復位時,SW RESET位等於0。

SCI Baud Rate Register

SCI的波特率來自低速預縮放器(LSPCLK)。

假設SYSCLK頻率為150MHz,低速預分頻器初始化為“除以4”,我們可以計算BRR的值,讓我們說數據速率為9600波特:

BRR必須是整數,因此我們必須將結果舍入到487. BRR = 487的反向計算導致實際數據速率為9605位/秒(誤差= 0.05%)。

SCI Control Register 2 – SCICTL2

位1和位0使能或禁止SCI發送和接收中斷。 如果不使用中斷,則可以通過清除第1位和第0位來禁用此功能。

在這種情況下,我們需要對發送器狀態標誌(SCICTL2.7和SCICTL2.6)應用輪詢方法。

SCITXEMPTY標誌等待整個數據幀離開SCI輸出,而標誌SCITXREADY表示我們可以在物理髮送前一個字符之前將下一個字符重新加載到SCITXBUF中。

接收器部分的狀態標誌可以在SCI接收器狀態寄存器中找到(參見下一張幻燈片)。

SCI Receiver Status Register – SCIRXST

SCI中斷邏輯在接收或發送完整字符時產生中斷標誌,由SCI字符長度決定。 這提供了一種方便有效的定時和控制SCI發送器和接收器操作的方法。 發送器的中斷標誌是TXRDY(SCICTL2.7),接收器的中斷標誌是RXRDY(SCIRXST.6)。 當字符傳輸到TXSHF並且SCITXBUF準備接收下一個字符時,TXRDY置位。 此外,當SCIBUF和TXSHF寄存器都為空時,TX EMPTY標誌(SCICTL2.6)置位。

當接收到新字符並轉入SCIRXBUF時,RXRDY標誌置位。 此外,如果發生中斷條件,則設置BRKDT標誌。 中斷條件是SCIRXD線在丟失停止位後保持連續低電平至少10位。 控制SCI操作的CPU可以輪詢上述每個標誌,或者通過將RX / BK INT ENA(SCICTL2.1)和/或TX INT ENA(SCICTL2.0)位置1有效來啟用與標誌相關的中斷高。

其他接收器錯誤存在附加標誌和中斷功能。 RX ERROR標誌是中斷檢測(BRKDT),幀錯誤(FE),接收器溢出(OE)和奇偶校驗錯誤(PE)位的邏輯或。 RX ERROR high表示在傳輸過程中發生了這四個錯誤中的至少一個。 如果RX ERR INT ENA(SCICTL1.6)位置1,這也會向CPU發送中斷請求。

SCI FIFO Mode Register

在增強功能集中,SCI模塊支持硬件中的自動波特率檢測邏輯。 以下部分介紹了自動波特率檢測功能的啟用順序。 自動波特率是一項功能,可用於將F2833x的數據速率調整為主機設備的傳輸速度。 如果主機發送字符'A'或'a',則自動波特率單元將鎖定此字符並相應地設置內部波特率寄存器。\

要使用此功能,需要遵循以下順序:

- 通過將SCIFFCT中的CDC位(位13)置1並通過向ABDCLR位(位14)寫1來清除ABD位(位15),為SCI啟用自動波特率檢測模式。

- 將波特率寄存器初始化為1或小於500 Kbps的波特率限制。

- 允許SCI以所需的波特率從主機接收字符“A”或“a”。如果第一個字符是“A”或“a”,則自動波特率檢測硬件將檢測輸入波特率並設置ABD位。

- 自動檢測硬件將使用十六進制的等效波特值更新波特率寄存器。邏輯還會產生CPU中斷。

- 通過向SCIFFCT寄存器的ABD CLR(第14位)寫入1來響應中斷清除ADB位,並通過寫入0清除CDC位來禁用進一步的自動波特率鎖定。

- 讀取字符“A”或“a”的接收緩衝區以清空緩衝區和緩衝區狀態。

- 如果在CDC為1時設置ABD(表示自動波特率校準),則會發生SCI發送FIFO中斷(TXINT)。中斷服務後,CDC位必須由軟件清零。

京公网安备 11010802041100号

京公网安备 11010802041100号