最近项目刚做完,利用难得的空闲时间写了一篇数字后端的面试题,希望对各位求职者有用。题目类型更偏向社招。对于社招,考官通常会更加注重工程师现场解决问题的能力,而并非基础概念的理解。

一共整理了100个题目。内容涵盖时序,功耗,PD,PV,工艺等方面,难度由简入繁,分为5个等级,难度指数说明如下:

1:常识,这个都回答不了的话回家先闭门思过啦。0~1年工作经验。

2:简单,面试前稍微准备一下应该都能回答。1~3年工作经验。

3:一般,稍微有一点难度,属于可能答不全的问题。3~5年经验。

4:较难,有难度的题目,通常要求有一定的综合性思考能力。5~7年经验

5:很难,非常有难度的题目,能回答出来基本都是后端专家了。7年经验以上。

小编水平有限,有的题目难免会有错,大家可以把这100个题目用做面试前的练习题。如果这100个问题都能解答的话,相信面试官会非常头疼了。觉得有用的朋友可以多多转发哦!

PS:题目顺序随机排列,更易记牢

1. 请说说最近项目中遇到的一些问题?最后是如何解决的?(综合性,难度2)

2. 这块芯片类型是什么?用了哪种工艺?规模有多大?(综合性,难度1)

3. 你负责芯片里哪几个模块,有多少instances和hard macro? (综合性,难度1)

4. 设计里面有哪些特殊IP,需要哪些特殊处理?遇到过哪些问题?(综合性,难度3)

5. Memory该如何摆放?说一说你知道的一些规则(Floorplan,难度3)

6. 摆放ICG cell时有什么注意事项?为什么ICG容易发生setup violation? (Place,难度3)

7. 在Place之后出现setup violation,应该从哪几方面考虑解决?(Place,难度2)

8. 你负责的模块里面有多少clock,频率可以跑到多少?(CTS,难度1)

9. 你的clock tree 的结构是怎样的?CTS是采用何种策略?func与test clock如何处理?(CTS,难度3)

10. 你在长tree时遇到最棘手的问题是什么?最后怎么解决的。(CTS,难度3)

11. 设计中碰到了哪些congestion的问题?通过什么方法解决的?(Route,难度3)

12. 讲一下修复setup和hold的方法,buf应该插在path的什么位置?(ECO,难度2)

13. 如何修复noise violation?(ECO,难度2)

14. Signoff使用了多少个timing corner? 列举一些(STA,难度2)

15. 列举几种setup和hold会出现互卡的情况?以及解决方法(ECO,难度3)

16. 你的项目里面有没有加timing derate?加了多少?为什么要加?(STA,难度3)

17. 这块芯片最后的功耗是多少?对降低芯片功耗采用了什么方法?(Power,难度3)

18. 如何修复IR-Drop, 你们公司signoff的静态动态IR drop是多少?(Power,难度2)

19. EM violation的形成原因,如何修复EM violation? (Power,难度3)

20. 介绍一下PV在项目中的流程, 每个阶段应该做什么事情?(PV,难度3)

21. CTS的时候采用了哪些约束?比如CTS使用的cell, skew设置, CTS的corner, max_transition设置, routing layer设置, 是否做了preplace。(CTS,难度2)

22. 怎么添加shileding,哪些clock需要做shielding?shielding的大致比例大致是多少?(CTS,难度3)

23. 一个scan chain有两个时钟域的DFF,一个时钟域的DFF有1000个,另一个时钟域的DFF只有两个。这个chain里有hold violation, 应该如何解决?(CTS,难度3)

24. 生长clock tree时,为什么优先采用inverter? (CTS,难度2)

25. High density区域的hold violation如何解决?(Place,难度3)

26. 为什么设计中一般不用最大和最小尺寸的cell? (Place,难度3)

27. 有什么方法可以压缩芯片面积?(Floorplan,难度4)

28. 当chip中有PLL/DDR等analog IP的时候,位置要怎么确定?有哪些需要注意的地方?(Floorplan,难度4)

29. 后端拿到前端网表时,通常要做哪些基本检查?给客户哪些反馈?(综合性,难度4)

30. 做过ARM的cpu吗?说说你遇到的ARM的cpu上的物理设计难点?(综合性,难度4)

31. 说一说routing使用double cut via的好处和缺点?(Route,难度3)

32. 你用过哪些timing ECO的工具?说说用到的一些特殊的option?(ECO,难度4)

33. 说一说你负责的block ,clock tree做到多长?列举一些可以减小clock latency的方法?(CTS,难度3)

34. POCV和AOCV的一些具体区别?(STA,难度2)

35. STA具体要负责哪些方面?(STA,难度4)

36. 功耗分为哪几类,分别和什么因素有关?(Power,难度4)

37. 谈一谈做过的先进工艺,与传统工艺有什么特殊的地方?从STA,PR,PV方面。(工艺,难度5)

38. 碰到formal fail的问题,后端应该如何debug? (formal,难度4)

39. 有没有使用脚本修复setup和hold的经验,介绍一下实现的方法?(Tcl,难度4)

40. 说一说power analysis的具体流程?(Power,难度3)

41. 请问下level shifter在H2L和L2H的情况下,需要插入在input端还是output端,有什么要求?(Power,难度4)

42. 解释一下PBA下path mode和exhaustive mode两种模式计算timing的区别?(STA,难度3)

43. 请说一下写sdc时有哪些方面需要注意的?(STA,难度4)

44. min pulse width violation的产生原因?如何修复它呢? (ECO,难度3)

45. 如果我把一块metal的宽度变成原来的两倍,电阻是不是会变成原来的一半?(Route,难度3)

46. 如果我需要做短clock tree,为什么不能全部clock tree用最大的cell去推?(CTS,难度2)

47. 解释一下IO buffer的作用(Place,难度2)

48. OSC为什么要靠近PLL摆放?(Floorplan,难度3)

49. 有没有做过flipchip的设计?说说摆放bump时应该考虑哪些因素?(Floorplan,难度4)

50. 简单介绍一下你自己吧?(我是来凑数的,难度1)

51. 说说为什么想要跳槽?(我是来凑数的,难度1)

52. 下面我们用英语聊会天吧。(我是来凑数的,难度2)

53. Memory之间的间距该如何确定?需要考虑哪些因素?(Floorplan,难度3)

54. 你的设计里有用到multibit FF么,有什么需要注意的要点?(Place,难度4)

55. 6层金属的工艺,你的block应该选择怎么样的形状?竖状or横条状?(Floorplan,难度3)

56. 如何提高芯片的频率,谈谈你有什么想法?(综合性,难度4)

57. 说一说你在以往项目中是怎么解决critical path的SI问题的?(Route,难度3)

58. Antenna violation是如何计算的,列举几种修复Antenna violation的方法? 往下跳线能不能解决?(ECO,难度4)

59. 使用useful skew 手动修复timing,需要考虑哪些条件?(ECO,难度3)

60. PR各个阶段采用了哪些timing corner?(STA,难度2)

61. sdc里面set_clock_group中, physical_exclusive, logically_exclusive, asynchronous三个option有什么区别,在计算noise时工具又会如何考虑他们?(STA,难度3)

62. 一条100um的导线延迟1ns,1000um的导线延迟是多少;如果每隔100um插一个buffer(延迟2ns),总延迟又是多少?(STA,难度3)

63. 分享一下你的power mesh设计经验?(Power,难度4)

64. 有没有做过低功耗设计?谈谈Low power有哪些方法。(Power,难度4)

65. Calibre中,VIRTUAL CONNECT 这个option在什么情况使用, signoff可以用吗? (PV,难度3)

66. 知道FDSOI工艺么,与其他工艺有什么区别,在layout上有啥不一样,能画个buffer的layout?(工艺,难度4)

67. Power switch的enable pin怎么接 ? (Power,难度3)

68. 请用sdc语句描述下面这段path,数值可以自己任意指定(STA,难度5)

69. set_disable_timing和set_false_path用法上有什么区别?(STA,难度2)

70. 如果through pin A的margin是100p,through pin B的margin是200p,那么through pin A和pinB的margin是多少?(ECO,难度2)

71. max transition, max cap, max fanout之间有什么相互关系?应该优先修复哪种violation? (ECO,难度3)

72. 如何完成RDL routing? 说说你的经验(Route,难度4)

73. 请解释下ignore pin, stop pin, exclude pin,并说说什么情况下会用到它们?(CTS,难度3)

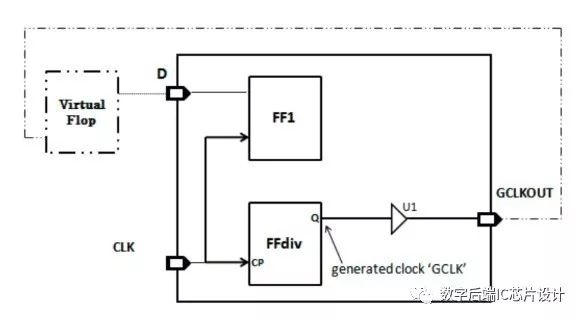

74. ICG cell的构造是怎么样的?为什么会发生ICG timing检查?有violation怎么解决?(CTS,难度3)

75. CTS工具是通过top down还是bottom up的方式来生成clock tree? (EDA,难度5)

76. 说一下你项目工艺中用到的一些特殊的Physical cell. (Place,难度4)

77. 做过异形的floorplan吗?遇到过哪些问题?(Floorplan,难度4)

78. top的IO摆放要考虑哪些因素?(Floorplan,难度5)

79. 做顶层时,需要block pd提供你哪些数据?(综合性,难度4)

80. 为什么要加decap cell,是不是加的越多越好?(Place,难度4)

81. ICG clone发生在CTS的什么阶段?(CTS,难度3)

82. 如果发现我摆的一个Floorplan有很多Routing的DRC,你会如何解决?假如这个Design的utilization大概是60%左右。(Route,难度3)

83. 如何去debug一些unconstraint, no clock的path? (STA,难度3)

84. 说一下crpr(cppr)对计算SI和OCV分别有什么影响?(STA,难度4)

85. ISO在各个power domain中如何添加,遵循什么原则?(Power,难度4)

86. LVS的时候发现source的port数量比layout的port数量少,该如何debug?(PV,难度3)

87. 知道body bias么?物理上如何实现连接? (工艺,难度3)

88. 请说一下PD每个阶段,uncertainty以及drv的一些设置考虑?(STA,难度3)

89. 修复hold时应该选用delay cell还是buffer?两者各有什么优缺点(ECO,难度2)

90. 为什么channel拐角的地方容易发生metal short? (Route,难度3)

91. 顶层的clock tree是怎么做的?和block 有什么区别?(CTS,难度5)

92. 你的设计里有用feedthrough么?说说是如何做的?(Floorplan,难度4)

93. 怎么提高design 的runtime ? 有什么见解?(综合性,难度4)

94. Setup和hold的计算是如何考虑SI的?(STA,难度2)

95. 跑full chip timing时,如何确保结果没问题呢,需要做哪些检查?(STA,难度4)

96. 知道Finfet工艺么?具体有什么特点,PR工具里有什么需要注意的?(工艺,难度4)

97. Analog ip的power能否给内部standard cell供电?为什么?(Power,难度3)

98. 如何初期评估一块芯片的面积,需要知道哪些条件?(Floorplan,难度4)

99. 某个模块的LVS报错,显示Incorrect net AVSS:VSS,VSS:AVSS,它们的物理连接和逻辑连接都没有错,分析一下可能的原因是什么? (PV,难度4)

100. 两条path有相同的hold violation,common path一条长,一条短,先修哪条?为什么?(ECO,难度5)

简历请戳邮箱:taozhang326[email protected]163.com

觉得有用的话,给我点个好看吧